Created

February 26, 2022 07:29

-

-

Save sago35/c30492647639458b9d90fec1ff28ad3b to your computer and use it in GitHub Desktop.

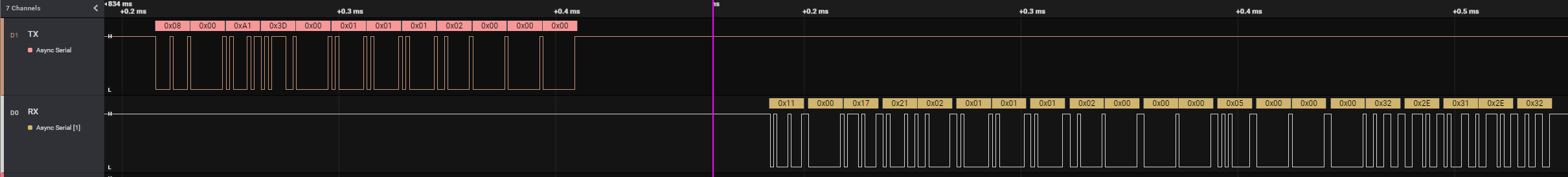

TinyGo で rtl8720dn との UART を TX:BCM1 RX:BCM2 に出力する設定

This file contains hidden or bidirectional Unicode text that may be interpreted or compiled differently than what appears below. To review, open the file in an editor that reveals hidden Unicode characters.

Learn more about bidirectional Unicode characters

| //go:build wioterminal | |

| // +build wioterminal | |

| package main | |

| import ( | |

| "device/sam" | |

| "machine" | |

| "runtime/interrupt" | |

| "time" | |

| "unsafe" | |

| dma "github.com/sago35/tinygo-dma" | |

| "tinygo.org/x/drivers/rtl8720dn" | |

| ) | |

| var ( | |

| uart UARTx | |

| uart2 *machine.UART | |

| desc2 *dma.DMADescriptor | |

| ) | |

| func handleInterrupt(interrupt.Interrupt) { | |

| // should reset IRQ | |

| uart.Receive(byte((uart.Bus.DATA.Get() & 0xFF))) | |

| uart.Bus.INTFLAG.SetBits(sam.SERCOM_USART_INT_INTFLAG_RXC) | |

| } | |

| func setupRTL8720DN() (*rtl8720dn.RTL8720DN, error) { | |

| setupCCL() | |

| machine.RTL8720D_CHIP_PU.Configure(machine.PinConfig{Mode: machine.PinOutput}) | |

| machine.RTL8720D_CHIP_PU.Low() | |

| time.Sleep(100 * time.Millisecond) | |

| machine.RTL8720D_CHIP_PU.High() | |

| time.Sleep(1000 * time.Millisecond) | |

| waitSerial() | |

| uart = UARTx{ | |

| UART: &machine.UART{ | |

| Buffer: machine.NewRingBuffer(), | |

| Bus: sam.SERCOM0_USART_INT, | |

| SERCOM: 0, | |

| }, | |

| } | |

| //uart.Interrupt = interrupt.New(sam.IRQ_SERCOM0_2, handleInterrupt) | |

| uart.Configure(machine.UARTConfig{TX: machine.PB24, RX: machine.PC24, BaudRate: 614400}) | |

| setupDMA() | |

| rtl := rtl8720dn.New(uart) | |

| debug = false | |

| rtl.Debug(debug) | |

| _, err := rtl.Rpc_tcpip_adapter_init() | |

| if err != nil { | |

| return nil, err | |

| } | |

| return rtl, nil | |

| } | |

| // Wait for user to open serial console | |

| func waitSerial() { | |

| for !machine.Serial.DTR() { | |

| time.Sleep(100 * time.Millisecond) | |

| } | |

| } | |

| type UARTx struct { | |

| *machine.UART | |

| } | |

| func (u UARTx) Read(p []byte) (n int, err error) { | |

| if uart2.Buffered() == 0 { | |

| time.Sleep(1 * time.Millisecond) | |

| return 0, nil | |

| } | |

| return uart2.Read(p) | |

| } | |

| func setupCCL() error { | |

| // UART2 (SERCOM0) TX -> BCM2 | |

| // BCM2 = PA17 // I2C Wire2 | |

| sam.GCLK.PCHCTRL[sam.PCHCTRL_GCLK_EVSYS0].SetBits(sam.GCLK_PCHCTRL_CHEN) | |

| for !sam.GCLK.PCHCTRL[sam.PCHCTRL_GCLK_EVSYS0].HasBits(sam.GCLK_PCHCTRL_CHEN) { | |

| } | |

| sam.GCLK.PCHCTRL[sam.PCHCTRL_GCLK_CCL].SetBits(sam.GCLK_PCHCTRL_CHEN) | |

| for !sam.GCLK.PCHCTRL[sam.PCHCTRL_GCLK_CCL].HasBits(sam.GCLK_PCHCTRL_CHEN) { | |

| } | |

| sam.MCLK.APBBMASK.SetBits(sam.MCLK_APBBMASK_EVSYS_) | |

| sam.MCLK.APBCMASK.SetBits(sam.MCLK_APBCMASK_CCL_) | |

| // /* Configure PORT */ | |

| sam.PORT.GROUP[0].DIRSET.Set(1 << 17) | |

| sam.PORT.GROUP[0].EVCTRL.Set(0x80 | 17) // PA17, OUT | |

| // /* Configure EVSYS */ | |

| sam.EVSYS.USER[1].Set(0x01) // Channel0 -> PORT_EV0 | |

| sam.EVSYS.CHANNEL[0].CHANNEL.Set(0x74 | (0x02 << 8) | (0x00 << 10)) // CCL_LUTOUT0, ASYNCHRONOUS, NO_EVT_OUTPUT | |

| // /* Configure CCL */ | |

| sam.CCL.CTRL.Set(1 << 0) // SWRST | |

| sam.CCL.SEQCTRL[0].Set(0x00) // Disable SEQCTRL | |

| sam.CCL.LUTCTRL[0].Set((0xAA << 24) | (0x01 << 22) | (0x09 << 8) | (0x01 << 1)) // TRUTH=0xAA, LUTEO, INSEL0=0x06(TC), ENABLE | |

| sam.CCL.CTRL.Set(1 << 1) // ENABLE | |

| return nil | |

| } | |

| func setupDMA() (*dma.DMA, error) { | |

| // UART2 (SERCOM0) RX -> SERCOM2 TX (PA12) | |

| // uart2 : sercom2 : pad0(tx) BCM1 PA12 : pad1(rx) BCM0 PA13 | |

| uart2 = machine.UART1 | |

| uart2.Configure(machine.UARTConfig{ | |

| TX: machine.PA12, | |

| RX: machine.PA13, | |

| BaudRate: 614400, | |

| }) | |

| dmarx := dma.NewDMA(func(d *dma.DMA) { | |

| return | |

| }) | |

| dmarx.SetTrigger(dma.DMAC_CHANNEL_CHCTRLA_TRIGSRC_SERCOM0_RX) | |

| dmarx.SetTriggerAction(sam.DMAC_CHANNEL_CHCTRLA_TRIGACT_BURST) | |

| desc2 = dma.NewDescriptor(dma.DescriptorConfig{}) | |

| desc2.UpdateDescriptor(dma.DescriptorConfig{ | |

| SRC: unsafe.Pointer(&uart.Bus.DATA.Reg), | |

| DST: unsafe.Pointer(&uart2.Bus.DATA.Reg), | |

| SRCINC: dma.DMAC_SRAM_BTCTRL_SRCINC_DISABLE, | |

| DSTINC: dma.DMAC_SRAM_BTCTRL_DSTINC_DISABLE, | |

| SIZE: uint32(1), // Total size of DMA transfer | |

| BLOCKACT: 1, | |

| DESC: unsafe.Pointer(desc2), | |

| }) | |

| dmarx.GetDescriptor().UpdateDescriptor(dma.DescriptorConfig{ | |

| SRC: unsafe.Pointer(&uart.Bus.DATA.Reg), | |

| DST: unsafe.Pointer(&uart2.Bus.DATA.Reg), | |

| SRCINC: dma.DMAC_SRAM_BTCTRL_SRCINC_DISABLE, | |

| DSTINC: dma.DMAC_SRAM_BTCTRL_DSTINC_DISABLE, | |

| SIZE: uint32(1), // Total size of DMA transfer | |

| BLOCKACT: 1, | |

| DESC: unsafe.Pointer(desc2), | |

| }) | |

| dmarx.Start() | |

| return dmarx, nil | |

| } |

Sign up for free

to join this conversation on GitHub.

Already have an account?

Sign in to comment

以下のようにすることで、 rtl8720dn から線だしせずに UART ログが取れるようになった。